Phase Change Memory: The new memory can be realized using a new memory model

Several important features from below, the phase-change memory (PCM) technology are in line with the current needs of electronic systems for the memory subsystem:

Capacity

- because of consumer electronics, computers, communications application trends triple, the amount of code that all electronic systems are growing at a rate of exponential data growth rate is even faster.

Bandwidth and energy consumption

- in the application of highly integrated electronic systems, in order to speed up the Internet speed, using bandwidth to measure system performance; enhancement products for mobile use, the use of power system performance evaluation. Memory must be designed to support the demand for expanded bandwidth and lower power consumption growing. A non-volatile solid-state memory is the best way to reduce power consumption.

Memory system

- in order to improve the overall performance of electronic systems, designers are increasingly concerned about the capacity of the memory system, technical performance, packaging and interface parameters.

Cache

- "memory system" does not support the concept of classification according to the memory technology, and support the bandwidth requirements of the final device according to memory classification, thus overcoming the memory technically design challenges, by temporarily retain and optimize the combination of different storage technologies to reduce product costs, improve system performance.

Bandwidth classification

from a higher level, we can consider three bandwidth categories: code, data flow and data storage.

Code

- read speed is the major determinant of code execution performance. When using one of the following modes, depending on the execution speed of code execution performance: execution (XIP) chip: the use of NOR flash requires a large bandwidth and random read speed; storage and downloading (S & D): the use of NAND + DRAM memory. S & D is a method of code storage capacity greater than 1Gb widely adopted.

Data streams

- data flows affect the performance of the main factors is the write speed. Stream usually DRAM technology, however, may be greater than the capacity of 4GB NAND + DRAM using a method is mainly used to increase capacity and reduce power consumption.

Data Storage

- affecting data storage performance is a major factor in memory capacity and data retention.However, due to the memory capacity growing at the rate of exponential growth, the delay between the different system components may affect the performance of the memory subsystem constitutes a big impact. 100GB capacity following high demands on performance or data storage commonly use NAND flash memory.

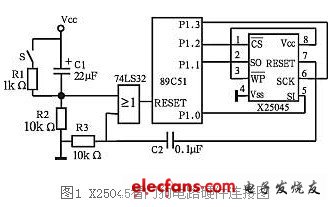

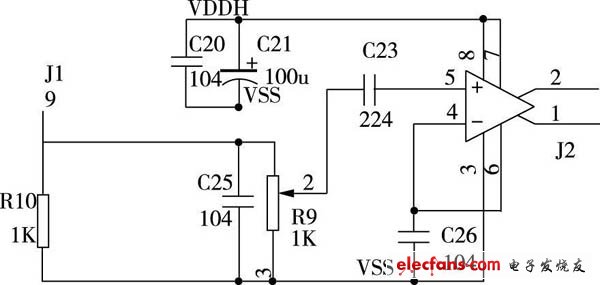

Figure 1 - high density memory technology overview

PCM upgrade capability

chalcogenide (PCM) application in at least three aspects of the film proved able to upgrade to at least PCM storage unit 5nm node. The main challenge facing the PCM technology upgrade is to upgrade the switch components. Because the state of research and improved control methods chalcogenide thin film materials, PCM-resistant ability to read and write and write speeds are expected in the near future there will be increased dramatically. With the process of the most advanced lithography techniques to enter the node, and write performance cost per PCM great progress is expected, because the storage unit in the nodes of these techniques can be made smaller.

PCM in embedded systems

in embedded systems, PCM is usually used to store data. Storage capacity requirements for lower system capacity is usually less than about 2Gb, designed to execute code directly from the flash memory NOR. In embedded systems, this memory is usually also used to store system files. Such systems typically act as a DRAM process using scratchpad.

In such systems, PCM used for code execution memory because it is a bit-erasable memory, PCM system can replace some of the DRAM needed.

In the "store and download memory" memory system, PCM can reduce capacity requirements for DRAM, but can also meet the capacity needs of the NAND. Meanwhile, the use of such systems in the PCM memory may be stored in the same memory to simplify the file system, and to improve file system performance.

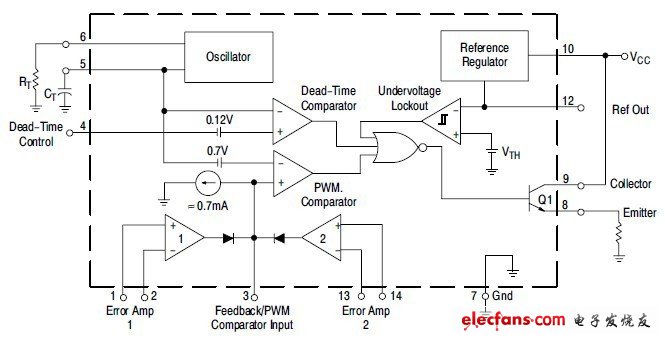

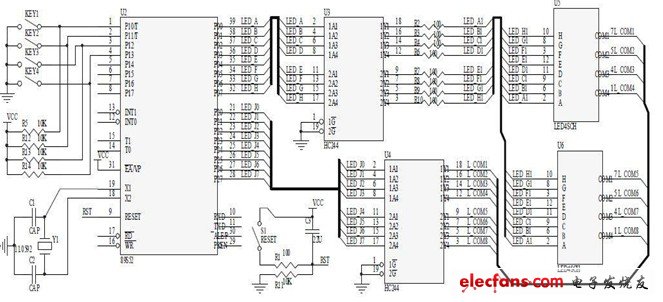

Figure 2 - SnD and XiP system architecture

PCM in a wireless communication system,

within a very short time delay to read quickly override function, PCM is an ideal non-volatile memory chip code execution solution from the low capacity to apply a variety of high-capacity storage applications. Although PCM read latency than DRAM long, but relatively small memory page read latency DRAM level or belong to, it can serve as a very good code execution memory.In addition to the data structure often operated, PCM can be used as a regular memory read all the data structures. PCM bit can erase function eliminates the need for block erase, while further reducing the demand for DRAM, thereby reducing the cost of the storage subsystem.

PCM is expected to become one of the lowest overall cost scalable memory subsystem solutions, while meeting the growing market demand for high-end multimedia wireless device performance.

Click to see image

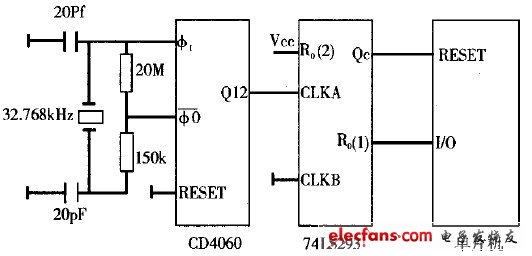

Figure 3 - PCM can improve the performance of advanced embedded systems, which has been proven in high-end wireless communications system

PCM in the solid state storage subsystem

because of the inherent characteristics of the block can be erased NAND technology, implemented in the solid-state storage subsystem Managing NAND is a big challenge. When a large number of erase operations or frequent read operations, memory error prone, leading to the need for error management mechanism, and error management mechanisms to meet the increasing demands of the market is also a challenge.

PCM processor can be saved in the solid-state storage systems frequently visited pages, as well as those operating data within the chip when more manageable elements, including NAND save data required parity, bad block table, block page mapping table and so on. In this case, the PCM can improve the manageability of NAND. By minimizing the NAND flash memory by the stress in the storage subsystem can achieve higher-capacity multi-level cell NAND flash memory using NAND PCM to reduce the cost function. This use as a PCM buffer solution will improve the performance and reliability of the storage subsystem.

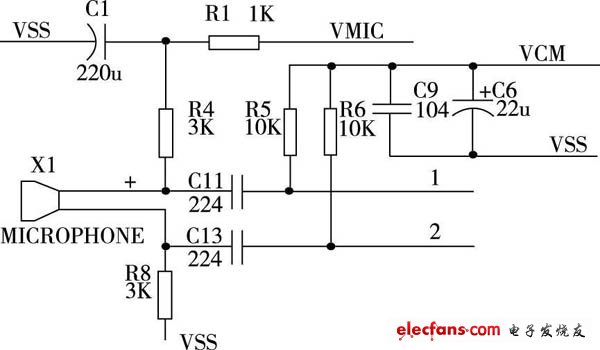

Figure 4 - mixing solid state memory

Further, when the dispersion of the erased pages in the plurality of blocks (nearly filled state), PCM can be further improved reliability of the storage subsystem. Management can block nearly filled state

Erase memory, you need to complete a number of erase cycles before for new data to be written to memory to free up space, and this will increase the endurance of memory, speed up the life of memory, up to a maximum endurance so far.

PCM bit can erase feature can solve the increased number of write cycles when the problem when the memory is full, the higher the number of read and write PCM systems can meet these requirements at the time of overload use.

PCM computer platform

as a volatile memory, DRAM requires a lot of energy stored content (W / GB). As a non-volatile memory, when the content does not need to PCM, PCM module can turn off the power, thereby reducing standby power consumption, more importantly, cut off contact between capacity and power consumption. This creates a capacity limit from PCM memory subsystem power limitation.In addition to the non-volatile external, PCM provides attractive for this application the ability to read and write delay resistance, compared with the current read and write frequently tried solution resistance, and the ability to read and write the write delay is a major advantage of PCM.

Conclusion The

PCM is a sustainable development and devastating memory technology has. From the viewpoint of complementarity, the two properties can accelerate market penetration of the PCM. In addition, PCM can be used for memory systems, and consumer electronics, computer, communications triple applications. This article also discusses some of the PCM storage systems to different penetration problems. Temporarily retain existing memory technologies, reducing overall system cost and system complexity, will be convincing motive recommend using PCM solutions.

In the code and data transmission applications, the bandwidth PCM will promote sustainable development, and low power consumption is another value-added feature of this technology.